半導體先進封裝(Advanced Packaging)是指一系列用於封裝半導體元件的技術,這些技術超越了傳統的封裝方法,一方面可提高晶片性能、縮小尺寸、降低功耗,在單一封裝內集合更多功能,另一方面也被認為是延續「摩爾定律」的解決方案。

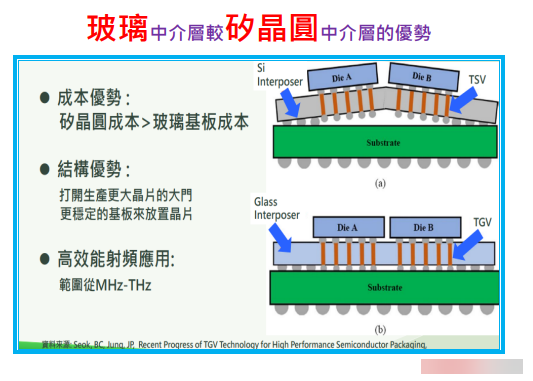

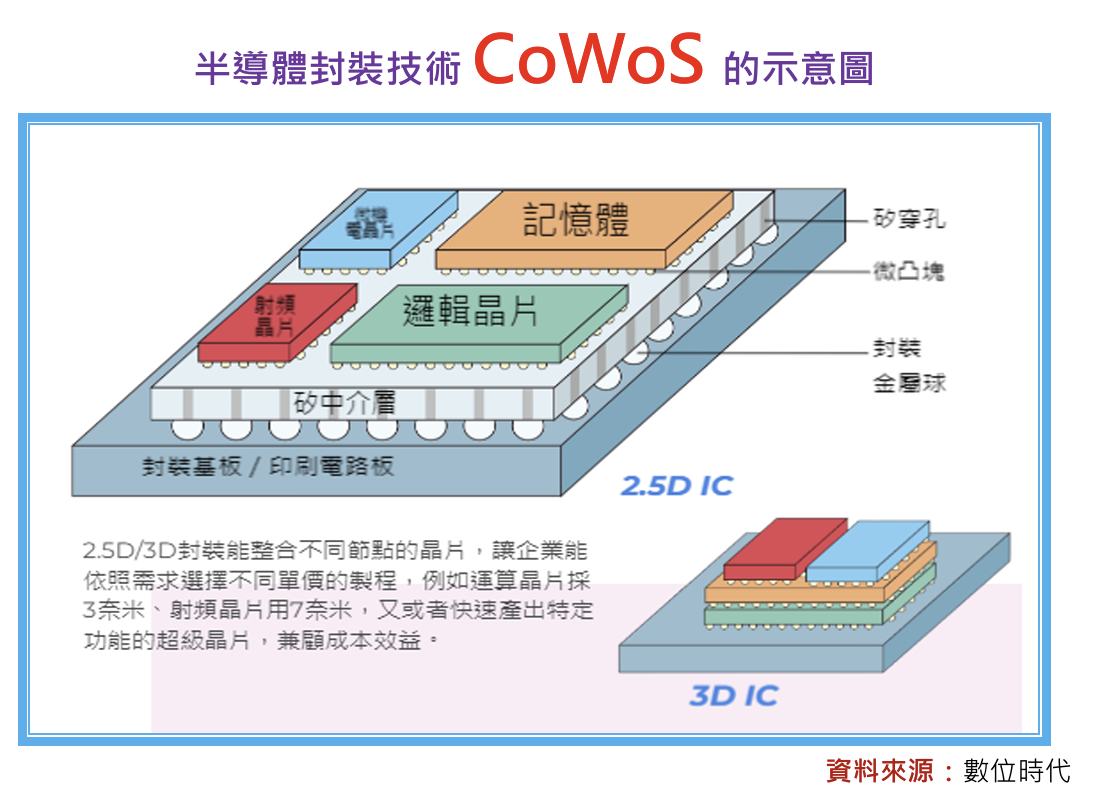

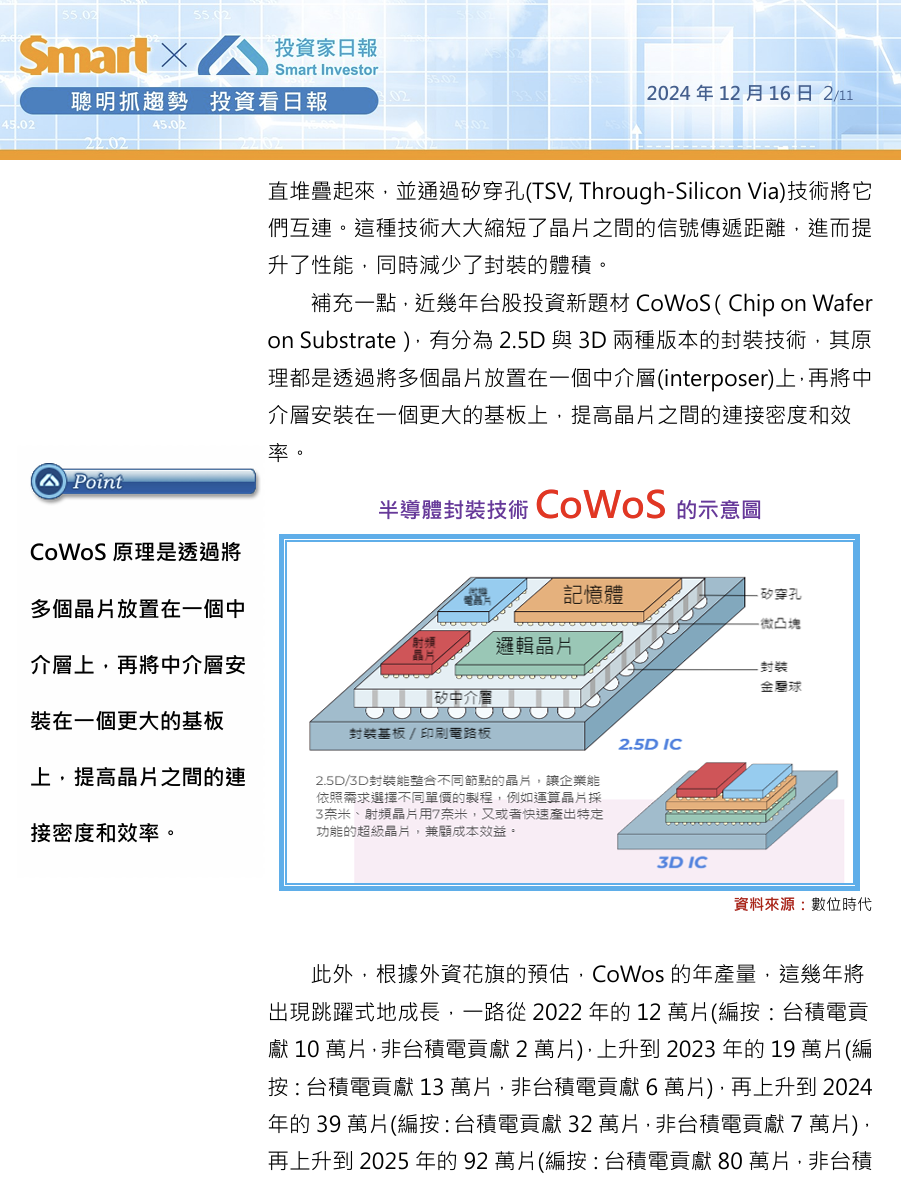

整體而言,半導體先進封裝的主要技術除了2.5D封裝之外,還有3D封裝,前者是將多個晶片(如處理器、記憶體)安裝在一個中介層(interposer)上,而中介層通常由矽晶圓或玻璃製成,可減少半導體晶片之間的延遲,並提高性能;後者是將多個晶片垂直堆疊起來,並通過矽穿孔(TSV, Through-Silicon Via)技術將它們互連。這種技術大大縮短了晶片之間的信號傳遞距離,進而提升了性能,同時減少了封裝的體積。

補充一點,近幾年台股投資新題材CoWoS(Chip on Wafer on Substrate),有分為2.5D與3D兩種版本的封裝技術,其原理都是透過將多個晶片放置在一個中介層(interposer)上,再將中介層安裝在一個更大的基板上,提高晶片之間的連接密度和效率。

此外,根據外資花旗的預估,CoWos的年產量,這幾年將出現跳躍式地成長,一路從2022年的12萬片(編按:台積電貢獻10萬片,非台積電貢獻2萬片),上升到2023年的19萬片(編按:台積電貢獻13萬片,非台積電貢獻6萬片),再上升到2024年的39萬片(編按:台積電貢獻32萬片,非台積電貢獻7萬片),再上升到2025年的92萬片(編按:台積電貢獻80萬片,非台積電貢獻12萬片),再上升到2026年的120萬片(編按:台積電貢獻100萬片,非台積電貢獻20萬片)。

換言之,2024年相較於2023年,年增率達到105%,2025年相較於2024年,年增率更攀升到135%。

本文From《投資家日報》2024年12/16

現在訂購,不但可加入日報專屬Line群

更可免費回看五天日報

【日報預覽圖】:

財報魔法師

孫慶龍

-

演講或合作事宜

daniel@sie.com.tw -

飆股基因Line

@smartapp -

投資家日報Line

@smart888